De temps à autre, dans la vie d’un processeur, des événements se produisent et provoquent des erreurs transitoires. Exemple classique : le rayonnement cosmique. Venue de l’espace, une particule traverse un circuit électronique et déclenche ce que l’on appelle un "bit flip". Brusquement, un bit de code binaire change de valeur. Il bascule de 0 à 1. Ou l’inverse. De quoi potentiellement entraîner un dysfonctionnement du logiciel.

Verbatim

Ce type de faute matérielle peut engendrer des conséquences dramatiques maintenant que l’IA (intelligence artificielle) effectue des tâches critiques sur des systèmes embarqués. Par exemple, on pourrait imaginer qu’une IA conduisant une voiture autonome se méprenne en croyant voir un oiseau, alors qu’il s’agit en fait… d’un piéton traversant la rue.

Professeur associée (Université de Rennes) - équipe TARAN

Pour maintenir la fiabilité matérielle malgré les "bit flips" et autres fautes transitoires, la méthode classique utilisée dans des domaines critiques comme l’aéronautique ou le spatial consiste à assurer une redondance par triplication. On effectue le même calcul trois fois. Si une valeur s’avère différente des deux autres, alors on la considère comme fausse. « Mais pour l’intelligence artificielle, cette méthode ne passe pas l’échelle. Trop de calculs. On ne peut pas tripler chacun d’entre eux. Ce serait trop coûteux. Sur les systèmes embarqués, on se doit de rester frugal. Il faut donc une nouvelle approche. Et c’est l’objectif de Re-Trusting. »

Financé par l’ANR, le projet est piloté par l’INL (Institut des nanotechnologies de Lyon - unité mixte de recherche CNRS, ECL, INSA Lyon, Université Lyon 1 et CPE Lyon). Outre Inria, il comprend aussi le Laboratoire informatique de Sorbonne Université (LIP6-CNRS) et Thales.

Maîtriser la tolérance aux fautes du hardware pour fiabiliser l’IA

Des accélérateurs matériels spécialisés

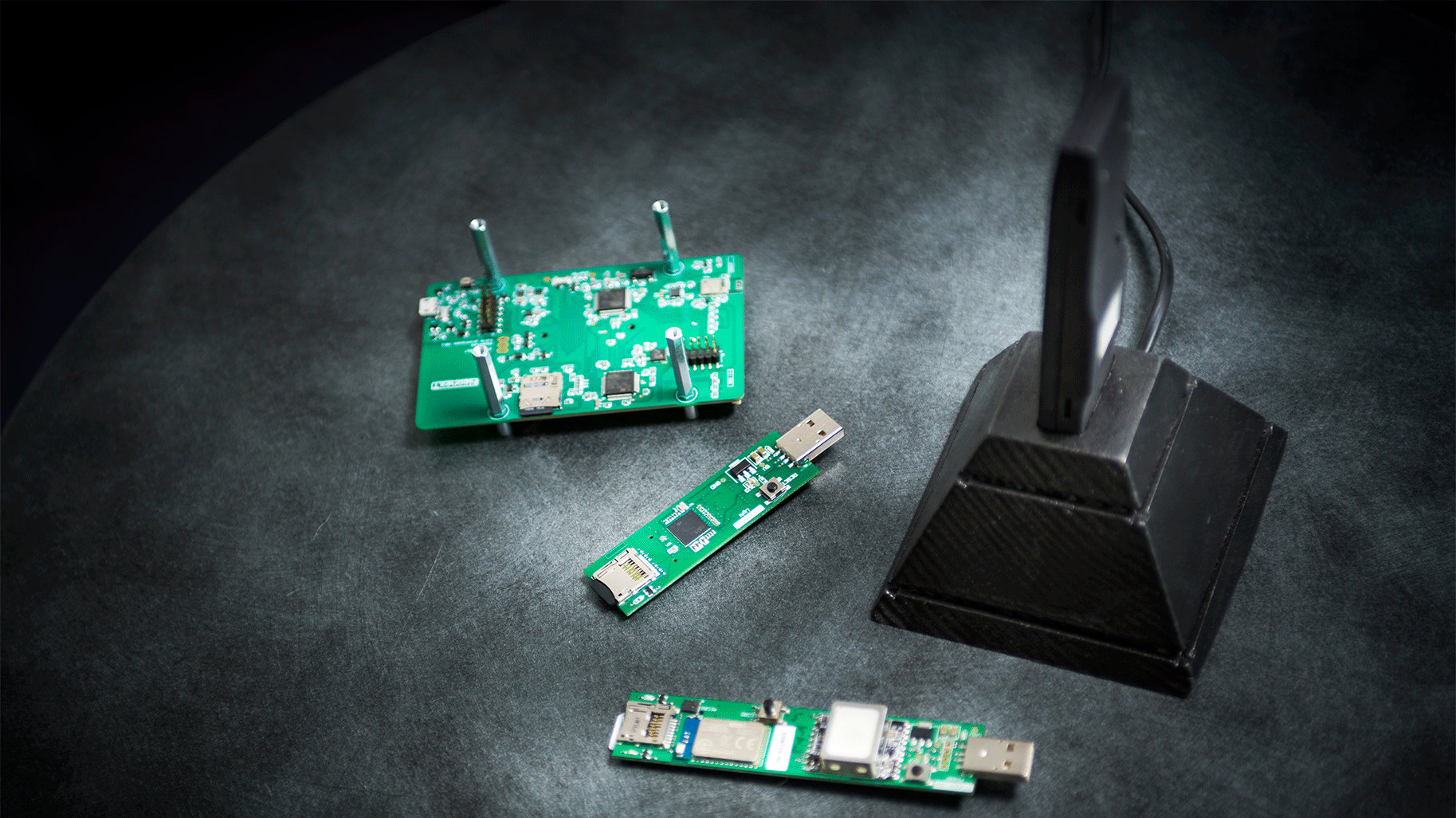

Ces recherches arrivent à un moment où de plus en plus d’applications IA quittent les serveurs centralisés du Cloud pour migrer vers le edge computing. Autrement dit : toutes les infrastructures périphériques du réseau, y compris les téléphones ou l’Internet des objets. Et cela, en particulier, pour s’affranchir des latences de communication. Épousant cette tendance, l’industrie des puces commence à produire des accélérateurs matériels spécialisés pour répondre aux gros besoins en calculs de ces algorithmes de deep learning désormais embarqués.

C’est précisément sur ces accélérateurs que le projet va se concentrer. « Nous en utilisons deux, précise le scientifique Inria Marcello Traiola. Le premier fourni par le LIP6. Le second par Thales. Nous disposons aussi de deux algorithmes différents de deep learning pour notre cas d’étude. D’une part, un réseau de neurones profond (Deep Neural Network – DNN). Et d’autre part, un réseau de neurones à impulsions (Spiking Neural Network – SNN). Fondamentalement, ils font la même chose, mais d’une façon légèrement différente. »

Verbatim

Notre premier objectif est de développer une méthodologie aussi générique que possible pour répondre à ce problème de comment estimer au mieux la fiabilité du système constitué par l’IA et le hardware.

Chargé de recherche Inria - équipe TARAN

Le point clé consiste à déterminer la gravité de la faute. Car sur ces immenses réseaux de neurones, toutes les erreurs hardware n’entraînent pas de graves conséquences. Beaucoup s’avèrent même bénignes. Les scientifiques voudraient donc produire un modèle d’analyse qui permettrait de cranter le degré de gravité de la faute. « À partir de là, nous pourrions utiliser les mécanismes habituels de tolérance aux fautes comme la triplication, mais en l’appliquant sélectivement aux endroits où c’est vraiment nécessaire. Ainsi, le coût supplémentaire lié à la protection resterait faible. »

Des accélérateurs matériels sépcialisés

Un champ difficile à explorer de par sa taille

Mais réussir une telle analyse reste un défi en soi. « L’espace à explorer est énorme. Ce serait difficile d’en parcourir la totalité. En revanche, aussi vaste que soit ce système, toutes les parties ne sont pas d’égale importance. Il faut donc trouver une approche intelligente et systématique pour identifier les points les plus importants de cet espace. Puis explorer ensuite localement ces endroits au maximum. » En pratique, ces travaux comportent une dimension expérimentale pour laquelle les chercheurs effectuent de l’injection de fautes par simulation logicielle.

« Pour avoir une compréhension complète de la propagation des fautes, il faut une analyse à plusieurs niveaux en partant du bas vers le haut, ajoute Angeliki Kritikakou. Le LIP6 se charge du plus bas niveau. C’est à dire les transistors, les portes logiques, etc. Quand tous ces composants seront caractérisés, Inria devra analyser l’impact au niveau algorithmique. Nous avons besoin en particulier de métriques qui, pour l’instant, n’existent tout simplement pas. À partir de ces résultats de recherche, INL travaillera ensuite à l’élaboration d’une série de mécanismes de protection du système IA+hardware. » Cela comprendra également des tests automatiques du système appuyés sur les nouvelles métriques de performance et les connaissances acquises en matière de sévérité des fautes.

Après quoi, Thalès se chargera d’intégrer ces nouveaux mécanismes dans les deux accélérateurs pour procéder ensuite à une phase d’évaluation. À la fin du projet, à l’automne 2025, le but est d’atteindre un taux de couverture de 100% sans dépasser 10% de surcoût énergétique et sans y allouer plus de 10% de la ressource matérielle.